Please select your location and preferred language where available.

鎧俠將於 IEDM 2024 發表新興記憶體技術

展示人工智慧、運算和儲存系統的創新應用

- 2024 年 10 月 21 日

- 鎧俠株式會社

全球記憶體解決方案領導廠商鎧俠株式會社今天宣布其研究論文已入選 2024 年國際電子元件會議 (IEDM),將在 12 月 7 日至 11 日期間於美國舊金山發表。

鎧俠致力於半導體記憶體的研發,這是人工智慧技術發展和社會數位轉型不可或缺的一部分。除了最先進的 3D 快閃記憶體技術 BiCS FLASH™之外,鎧俠還擅長新興記憶體解決方案的研究。該公司持續努力推出創新的記憶體產品,以滿足未來運算和儲存系統的需求。

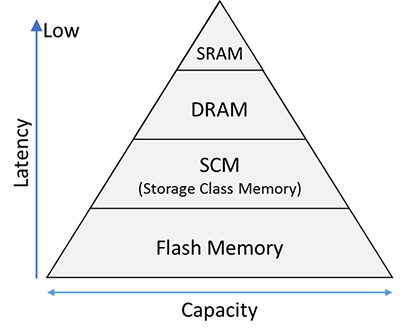

現有的運算系統利用 DRAM 作為主要的記憶體裝置,讓 CPU 能夠快速處理資料,並搭配快閃記憶體來儲存大量資料。鎧俠在儲存級記憶體 (SCM) 的研發方面引領業界。SCM 是在半導體記憶體階層中位於 DRAM 和快閃記憶體之間的記憶體解決方案,旨在處理比 DRAM 更大的資料量,且速度比快閃記憶體更快。

圖:記憶體階層

鎧俠將在 IEDM 上發表針對這三種半導體記憶體層中量身打造的尖端技術:(1) 一種採用氧化物半導體的新型 DRAM,專注於降低功耗;(2) 適合較大 SCM 應用容量的 MRAM;以及 (3) 一種具有卓越位元密度和效能的 3D 快閃記憶體新結構。

新興記憶體技術:

- 氧化物半導體通道電晶體 DRAM (OCTRAM):

這項技術是由南亞科技和鎧俠株式會社共同開發。兩家企業開發的垂直電晶體,可透過改善製程來強化電路整合。它們利用氧化物半導體來發揮電晶體的特性,進而達成極低的漏電流。這可能會降低各種應用的功耗,包括 AI 和後 5G 通訊系統及 IoT 產品。

論文標題:採用 4F2 架構的氧化物半導體通道電晶體 DRAM (OCTRAM) (論文編號:6-1)

- 高容量交叉點型 MRAM 技術:

這項技術是由 SK 海力士半導體公司和鎧俠株式會社共同開發。此技術透過將大容量選擇器與磁隧道接合點配對的單元技術,同時將精細加工技術應用於交叉點式陣列,以 20.5 奈米的 MRAM 單元半間距實現最小規模的單元讀取/寫入操作。隨著單元小型化,記憶體可靠性通常會下降。兩家企業開發出潛在的解決方案,透過一種新的讀取方法利用選擇器的瞬態反應,並減少讀出電路的寄生電容。這項技術具備人工智慧和大數據處理的實際應用。

論文標題:適用於 64 Gb 交叉點型 MRAM 的全球最小 1Selector-1MTJ 單元以低讀取干擾率維持可靠記憶體運作(論文編號:20-1)

- 具有水平單元堆疊結構的新一代 3D 記憶體技術:

鎧俠開發了新的 3D 結構,以提高可靠性並防止 NAND 型單元效能下降。當傳統結構的堆疊層數增加時,通常會發生效能下降的情況。與垂直排列 NAND 型單元的傳統結構相比,新結構透過堆疊的方式水平排列 NAND 型單元。此結構能以低成本實現具備高位元密度且可靠的 3D 快閃記憶體。

論文標題:進階水平通道快閃記憶體的卓越可擴充性,適用於未來世代的 3D 快閃記憶體(論文編號:30-1)

如需 IEDM 的詳細資訊,請造訪:https://www.ieee-iedm.org/

鎧俠秉持「透過『記憶體』提升世界」的使命,致力以記憶體技術開創新的時代,並持續促進支援未來數位社會的研究和技術開發。

本文件資訊包括產品價格、規格、服務內容與聯絡資訊在發佈日期時正確無誤,如有變更,恕不另行通知。